세계 최대 규모 첨단 복합 라인

D램 양산 시작, 차세대 V낸드, 초미세 파운드리 제품 생산 예정

축구장 16개 크기 미래 반도체 생산 거점

총 30조원 이상 대규모 투자 집행 예정, 3만명 이상 고용창출 기대

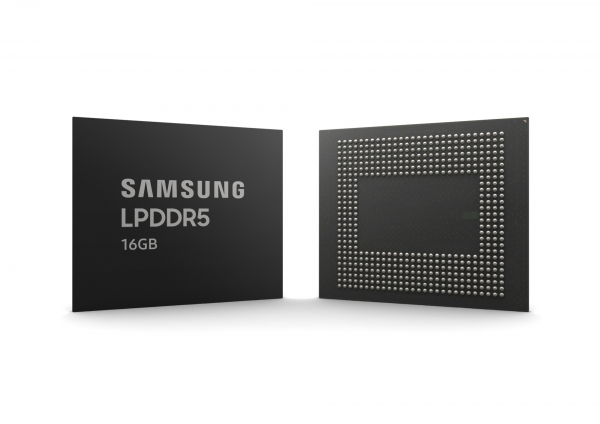

업계 최초 EUV 공정 적용한 3세대 10나노급(1z) 16Gb LPDDR5 출하

[중소기업투데이 황복희 기자] 삼성전자가 세계 최대 규모의 반도체 공장인 평택 2라인 가동에 들어갔다. 4차 산업혁명 시대의 반도체 초격차 달성을 위한 첨단 복합 라인이다. 업계 최초로 EUV(Extreme Ultraviolet·극자외선) 공정을 적용한 첨단 3세대 10나노급(1z) LPDDR5 모바일 D램이 생산된다. D램 양산을 시작으로 차세대 V낸드, 초미세 파운드리 제품이 생산될 예정이다.

연면적 12만9000㎡(축구장 16개) 크기의 미래 반도체 생산 거점인 셈이다. 삼성전자는 이곳에 총 30조원 이상의 대규모 투자를 집행할 예정이다. 직접 고용 인력 약 4000명을 비롯해 협력사 인력과 건설인력을 포함해 약 3만명 이상의 고용창출이 기대된다.

D램, 낸드, 파운드리까지 생산하는 세계 최대 반도체 생산 라인

삼성전자는 평택 2라인에 지난 5월 EUV 기반 최첨단 제품 수요에 대비하기 위한 파운드리 생산라인을 착공했다. 이어 6월에는 첨단 V낸드 수요 확대에 대응하기 위한 낸드플래시 생산라인도 착공했다. 두 라인 모두 2021년 하반기부터 본격 가동할 예정이다.

이번 평택 2라인은 지난 2018년 8월 발표한 180조원 투자, 4만명 고용 계획의 일환으로 건설됐다.

지난 2015년부터 조성된 평택캠퍼스는 289만㎡의 부지를 가진 삼성전자의 차세대 반도체 전초기지다. 평택 1라인은 2017년 6월 양산을 시작했고, 평택 2라인은 2018년 1월 착공돼 이번에 처음으로 D램 제품을 출하했다.

차세대 스마트폰 시장 선점할 최첨단 EUV D램 본격 양산

평택 2라인에서 이번에 출하된 16Gb LPDDR5 모바일 D램은 메모리 양산제품으로는 처음 EUV 공정이 적용됐다. 역대 최대 용량과 최고 속도를 동시에 구현한 업계 최초의 3세대 10나노(1z) LPDDR5 제품이다.

삼성전자는 지난 2월 2세대 10나노급(1y) 공정으로 역대 최대 용량의 16GB(기가바이트) LPDDR5 D램을 양산한지 6개월만에 차세대 1z 공정까지 프리미엄 모바일 D램 라인업을 강화했다.

이번 제품은 기존 플래그십 스마트폰용 12Gb 모바일 D램(LPDDR5, 5500Mb/s)보다 16% 빠른 6400Mb/s의 동작속도를 구현했다. 16GB 제품 기준으로 1초당 풀HD급 영화(5GB) 약 10편에 해당하는 51.2GB(기가바이트)를 처리할 수 있다. (동작속도: 64핀(x64, JEDEC 규격)으로 구성되는 패키지 기준 최대 51.2GB/s)

또한 16Gb LPDDR5 모바일 D램은 8개의 칩만으로 16GB 제품을 구성할 수 있어 기존 제품(12Gb 칩 8개+8Gb 칩 4개)대비 30% 더 얇은 패키지를 만들 수 있다. 이를 통해 멀티카메라, 5G 등 부품수가 많은 스마트폰과 폴더블폰 같이 두께가 중요한 제품에 최적의 솔루션을 제공한다.

삼성전자는 글로벌 스마트폰 업체들에게 차세대 1z 16GB 모바일 D램을 업계 유일하게 제공함으로써 내년 출시되는 AI기능이 더욱 강화된 5G 플래그십 스마트폰 시장을 선점할 계획이다. 또 고온 신뢰성도 확보해 전장용 제품까지 사용처를 확대해 나갈 예정이다.

삼성전자 메모리사업부 DRAM개발실 이정배 부사장은 “이번 1z나노 16Gb LPDDR5는 역대 최고 개발 난도를 극복하고 미세공정 한계 돌파를 위한 새로운 패러다임을 제시한 제품”이라며 “프리미엄 D램 라인업을 지속 확대해 고객 요구에 더욱 빠르게 대응하고 메모리 시장을 확대해 나갈 것”이라고 말했다.

<삼성전자 최첨단 D램 상용화 연혁>

▲2009.07월 40나노급 2Gb DDR3 양산

▲2010.02월 40나노급 4Gb DDR3 양산

▲2010.07월 30나노급 2Gb DDR3 양산

▲2011.09월 20나노급(2x) 2Gb DDR3 양산

▲2012.11월 20나노급(2y) 4Gb DDR3 양산

▲2013.11월 20나노급(2y) 6Gb LPDDR3 양산

(※ 2014.02월 20나노급(2y) 8Gb LPDDR4 양산)

▲2014.02월 20나노(2z) 4Gb DDR3 양산

▲2014.10월 20나노(2z) 8Gb DDR4 양산

▲2014.12월 20나노(2z) 8Gb LPDDR4 양산

▲2014.12월 20나노(2z) 8Gb GDDR5 양산

▲2015.08월 20나노(2z) 12Gb LPDDR4 양산

▲2016.02월 1세대 10나노급(1x) 8Gb DDR4 양산

▲2016.09월 1세대 10나노급(1x) 16Gb LPDDR4/4X 양산

▲2017.11월 2세대 10나노급(1y) 8Gb DDR4 양산

▲2019.03월 3세대 10나노급(1z) 8Gb DDR4 개발

▲2019.06월 2세대 10나노급(1y) 12Gb LPDDR5 양산

▲2019.09월 3세대 10나노급(1z) 8Gb DDR4 양산

▲2020.03월 4세대 10나노급(1a) D램(EUV) 개발

▲2020.03월 1세대 10나노급(1x) D램(EUV) 샘플 100만개 공급

▲2020.08월 3세대 10나노급(1z) 16Gb LPDDR5(EUV) 양산

▲2021년 4세대 10나노급(1a) 16Gb DDR5/LPDDR5(EUV) 양산 예정